Sekvenčné logické obvody: Rozdiel medzi revíziami

Z SensorWiki

(→Simulátor) |

(→Analýza) |

||

| Riadok 2: | Riadok 2: | ||

== '''Analýza''' == | == '''Analýza''' == | ||

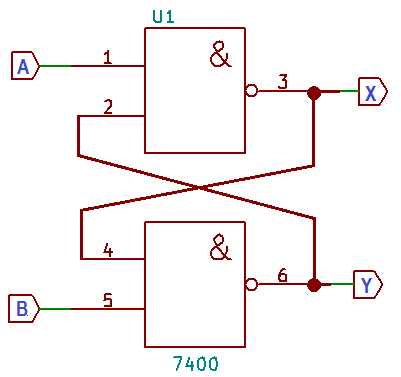

| − | Analyzujte preklápací obvod zostavený z dvoch členov NAND podľa nasledovného zapojenia: | + | 1. Analyzujte preklápací obvod zostavený z dvoch členov NAND podľa nasledovného zapojenia: |

[[Súbor:RS-FlipFlopNAND.png]] | [[Súbor:RS-FlipFlopNAND.png]] | ||

| Riadok 9: | Riadok 9: | ||

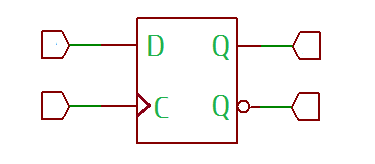

| − | + | 2. Analyzujte preklápací obvod typu D (v programe Simulator.IO sa volá FF): | |

| + | |||

| + | [[Súbor:FlipFlopD.png]] | ||

| + | |||

| + | Pri simulovaní s výhodou využijete generátor impulzu. | ||

| + | Vypracujte pravdivostnú tabuľku, stavový diagram a časový diagram. | ||

| + | |||

== '''Syntéza''' == | == '''Syntéza''' == | ||

Verzia zo dňa a času 13:29, 23. október 2017

Analýza

1. Analyzujte preklápací obvod zostavený z dvoch členov NAND podľa nasledovného zapojenia:

Vypracujte pravdivostnú tabuľku, stavový diagram a časový diagram.

2. Analyzujte preklápací obvod typu D (v programe Simulator.IO sa volá FF):

Pri simulovaní s výhodou využijete generátor impulzu. Vypracujte pravdivostnú tabuľku, stavový diagram a časový diagram.

Syntéza

- Domáca úloha z prednášky: vydelili ste? Všimli ste si niečo?

Navrhnite obvod pre delenie 2,4 a 8.

- Navrhnite deličku frekvencie 4

Vypracujte pravdivostnú tabuľku, stavový diagram a časový diagram.

- Navrhnite posuvný register dĺžky 8 s posuvom vľavo

- Navrhnite binárne počítadlo 0 - 16

Simulátor

- na simulátore zostavte RS obvod z členov NAND a overte jeho funkciu podľa tabuľky

- vytvorte model deličky 2 a 4

- vytvorte model 4-bitového počítadla

- vytvorte model posuvného registra

- Link do simulátora.IO