Kombinačné logické obvody: Rozdiel medzi revíziami

Zo stránky SensorWiki

dBez shrnutí editace |

|||

| (18 medziľahlých úprav od rovnakého používateľa nie je zobrazených.) | |||

| Riadok 3: | Riadok 3: | ||

Teória: [http://www2.fiit.stuba.sk/~kvasnicka/Logika/Lecture09/09.prezentacia.pdf Logické obvody] | Teória: [http://www2.fiit.stuba.sk/~kvasnicka/Logika/Lecture09/09.prezentacia.pdf Logické obvody] | ||

=== '''Analýza''' === | |||

Hint: v prehliadači Microsoft Edge si môžete písať poznámky priamo do schémy zapojenia. | |||

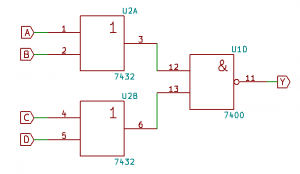

1. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu | 1. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu | ||

| Riadok 12: | Riadok 11: | ||

[[Súbor:LogickeObvody01.png|300px]] | [[Súbor:LogickeObvody01.png|300px]] | ||

2. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu | 2. Vypracujte pravdivostnú tabuľku a nakreslite schému pre logickú funkciu | ||

<math>Y = \overline{A.B} . (\overline{C+D})</math> | |||

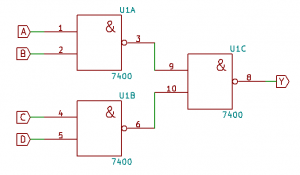

3. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu | |||

[[Súbor:LogickeObvody02.png|300px]] | [[Súbor:LogickeObvody02.png|300px]] | ||

4. Vypracujte pravdivostnú tabuľku a nakreslite schému pre logickú funkciu | |||

<math>Y = \overline{A+B} + \overline{C} + (\overline{C.\overline{D}})</math> | |||

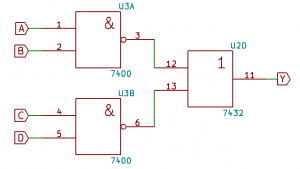

5. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu | |||

[[Súbor:LogickeObvody03.png|300px]] | [[Súbor:LogickeObvody03.png|300px]] | ||

| Riadok 23: | Riadok 28: | ||

{Kontrolná otázka: Pre ktorú kombináciu vstupov ABCD bude na výstupe '''log. 0'''? | {Kontrolná otázka: Pre ktorú kombináciu vstupov ABCD bude na výstupe '''log. 0'''? | ||

|type="[]"} | |type="[]"} | ||

+ 1111 | |||

- 1010 | - 1010 | ||

- 0101 | - 0101 | ||

- 0000 | |||

</quiz> | </quiz> | ||

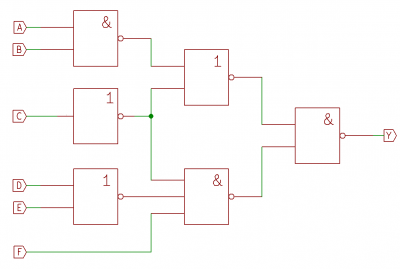

6. na schéme zapojenia určte hodnotu výstupu pre dané vstupy | |||

[[Súbor:LogickeObvody10.png|400px]] | [[Súbor:LogickeObvody10.png|400px]] | ||

| Riadok 36: | Riadok 41: | ||

{Aký bude výstup pre kombináciu ABC DEF = '''010 110'''? | {Aký bude výstup pre kombináciu ABC DEF = '''010 110'''? | ||

|type="()"} | |type="()"} | ||

+ | - 0 | ||

+ 1 | |||

{Aký bude výstup pre kombináciu ABC DEF = '''101 111'''? | {Aký bude výstup pre kombináciu ABC DEF = '''101 111'''? | ||

|type="()"} | |type="()"} | ||

+ | - 0 | ||

+ 1 | |||

{Aký bude výstup pre kombináciu ABC DEF = '''000 111'''? | {Aký bude výstup pre kombináciu ABC DEF = '''000 111'''? | ||

|type="()"} | |type="()"} | ||

+ | - 0 | ||

+ 1 | |||

</quiz> | </quiz> | ||

| Riadok 77: | Riadok 82: | ||

</quiz> | </quiz> | ||

=== '''Syntéza''' === | |||

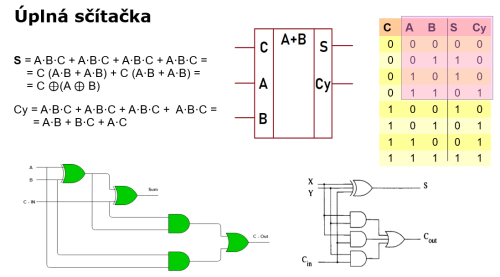

# navrhnite obvod realizujúci polovičnú a úplnú sčítačku - zadané tabuľkou alebo funkciou | |||

=== '''[https://simulator.io/ Simulátor]''' === | |||

Simulátor nájdete na adrese [https://simulator.io/ simulator.io] | |||

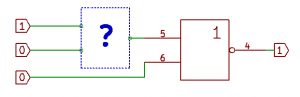

# na simulátore zostavte obvod XOR zo štyroch hradiel NAND (prednáška) a overte jeho funkciu podľa tabuľky | |||

[[Image:NAND_XORschema.png|Schéma zapojenia|500px]] | |||

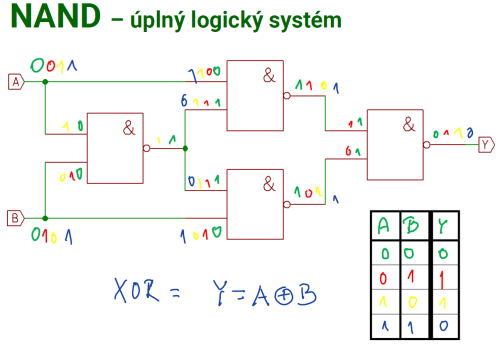

# vytvorte model polovičnej sčítačky podľa prednášky a overte jeho funkciu | |||

[[Image:HalfAdderSchema.png|Schéma zapojenia|500px]] | |||

# vytvorte model úplnej sčítačky a overte jeho funkciu | |||

[[Image:FullAdderSchema.png|Schéma zapojenia|500px]] | |||

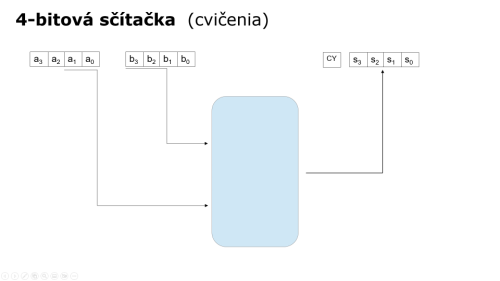

# vytvorte model 4-bitovej sčítačky | |||

[[Image:4-bitAdderSchema.png|Schéma zapojenia|500px]] | |||

<BR><BR> | |||

=== Testík === | |||

# 15 min. pred koncom cvičenia sa prihláste do AISu a vypracujte test | # 15 min. pred koncom cvičenia sa prihláste do AISu a vypracujte test | ||

=== Na voľné chvíle === | |||

<html> | <html> | ||

Aktuálna revízia z 11:37, 6. október 2025

Cvičenie 4

Teória: Logické obvody

Analýza

Hint: v prehliadači Microsoft Edge si môžete písať poznámky priamo do schémy zapojenia.

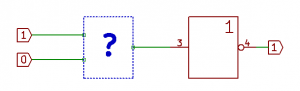

1. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu

2. Vypracujte pravdivostnú tabuľku a nakreslite schému pre logickú funkciu

3. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu

4. Vypracujte pravdivostnú tabuľku a nakreslite schému pre logickú funkciu

5. ku schéme zapojenia vypracujte pravdivostnú tabuľku a určte logickú funkciu

6. na schéme zapojenia určte hodnotu výstupu pre dané vstupy

5. doplňte do schémy zapojenia log. obvod tak, aby výstup mal požadovanú hodnotu

5. doplňte do schémy zapojenia log. obvod tak, aby výstup mal požadovanú hodnotu

Syntéza

- navrhnite obvod realizujúci polovičnú a úplnú sčítačku - zadané tabuľkou alebo funkciou

Simulátor

Simulátor nájdete na adrese simulator.io

- na simulátore zostavte obvod XOR zo štyroch hradiel NAND (prednáška) a overte jeho funkciu podľa tabuľky

- vytvorte model polovičnej sčítačky podľa prednášky a overte jeho funkciu

- vytvorte model úplnej sčítačky a overte jeho funkciu

- vytvorte model 4-bitovej sčítačky

Testík

- 15 min. pred koncom cvičenia sa prihláste do AISu a vypracujte test

Na voľné chvíle

|

|

Circuit Scramble Hra s logickými obvodmi na Android |

|