1-Riadková kamera TSLR1401: Rozdiel medzi revíziami

Z SensorWiki

| Riadok 241: | Riadok 241: | ||

<center>'''Obr. 6.''' Zaznamenaný priebeh signálu A0 pomocou kamery TSL1410_DB</center> | <center>'''Obr. 6.''' Zaznamenaný priebeh signálu A0 pomocou kamery TSL1410_DB</center> | ||

| + | === Záver === | ||

| + | ---- | ||

Verzia zo dňa a času 16:02, 22. december 2012

- Vypracovali:

- Bc. Peter Lovaš

- Bc. Tomáš Oravec

- Bc. Ján Mazúch

- Študijný odbor: Aplikovaná mechatronika

- Ročník: 2. Ing.

Zadanie úlohy

- Riadkovy senzor TSL1410_DB pripojte k mikroprocesoru, výstupný analógový signál preneste do PC a zobrazte.

Popis riadkovej kamery

TSL1401_DB je lineárna kamera, ktorá sa skladá z poľa fotodiód 128 x 1. Vnútorná riadiaca logika kamery si vyžaduje pre správnu funkčnosť zapojenie sériového vstupu SI a hodinového signálu CLK.

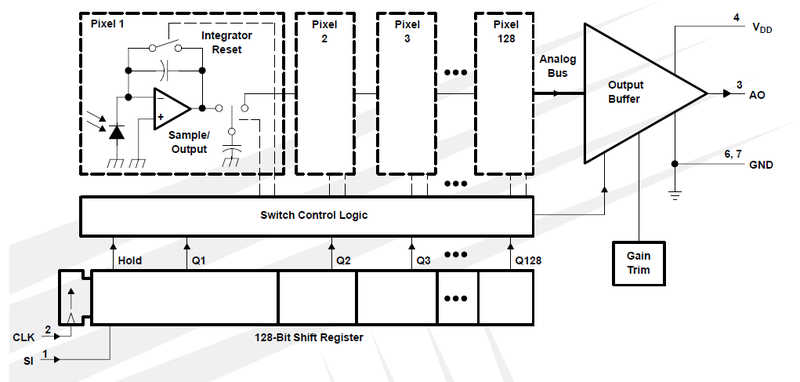

Na nasledujúcom obrázku je schéma vnútornej štruktúry lineárnej kamery a označenie jednotlivých pinov.

Označenie jednotlivých pinov a popis:

- PIN A0_3 - analógový výstup

- PIN CLK_2 - hodiny, riadia prenos, pixelový výstup a reset

- PIN GND_6,7 - zem

- PIN SI_1 - sériový vstup, definuje počiatok vysielania dát

- PIN VDD_4 - napájacie napätie pre analógové aj digitálne obvody

Popis činnosti:

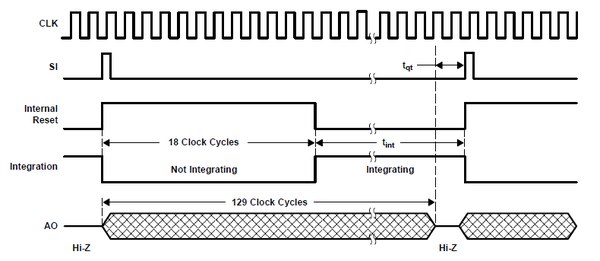

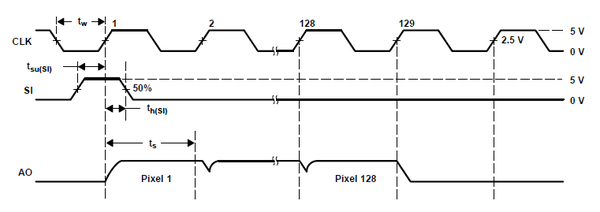

Kamera sa skladá zo 128 fotodiód usporiadaných v lineárnom poli. Svetelná energia, ktorá dopadá na každú jednu fotodiódu(jeden pixel) vytvára na každej tejto fotodióde prúd. Počas integračného času sa kondenzátor pripojí k výstupu integrátora prostredníctvom analógového prepínača. Náboj nahromadený na každom pixeli(fotodióde) je priamoúmerný intenzite osvetlenia a integračného času. Výstup a Reset integrátorov je riadený 128-bitovým posuvným registrom. Výstupný cyklus(posielanie dát)je inicializovaný, ak je na pine SI logická 1. Počas prvých 18 hodinových cyklov neprebieha integrácia. Integrácia a prenos dát začína až po uplynutí 18 hodinových cyklov. Rozsah napájania lineárnej kamery je VDD = 3 - 5,5V.

Vypracovanie

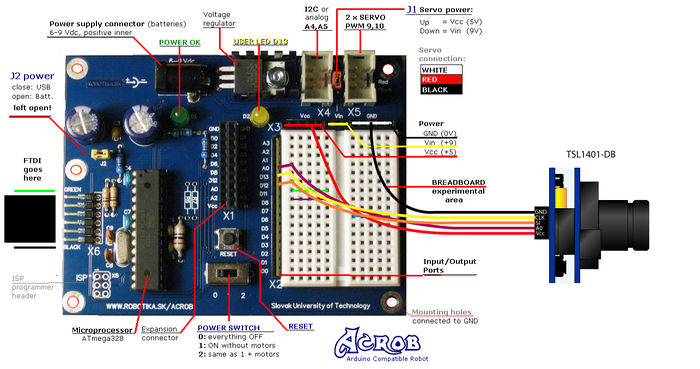

Pripojenie kamery k Acrob doske a definovanie pinov je v hlavičkovom súbore "kamera.h". Rýchlosť sériového portu je nastavená na 19200 Baud/rate. Na začiatku sa vyšlú konfiguračné príkazy do Stampplotu, stačí zaškrtnúť "plot data" a potom "connect". Pred spustením treba držať reset na doske, aby sa začali vysielať dáta až po pripojení. Nastavenie integračného času je vyriešené tak, že po prijatí 1 znaku sa jeho hodnota 0 až 255 nastaví ako integračný čas v milisekundách (strop je obmedzený na 100),dá sa pozmeniť v zdrojovom kóde.

Schéma zapojenia kamery:

Nami definovaná knižnica:

#ifndef KAMERA_H_

#define KAMERA_H_

#define CLK_PORT B

#define CLK_PIN 5

#define SI_PORT B

#define SI_PIN 4

#define A0_PORT C

#define A0_PIN 0

#endif /* KAMERA_H_ */

Zdrojový kód v jazyku C:

#include <stdio.h>

#include <avr/io.h>

#include <avr/interrupt.h>

#include <util/delay.h>

#include "kamera.h"

/* Global macros */

#define sbit(var, bit) var |= (1 << bit);

#define cbit(var, bit) var &= ~(1 << bit);

#define rbit(var, bit) ((var & (1 << bit)) != 0)

#define CONCAT(a, b) a ## b

#define DDR(port) CONCAT(DDR, port)

#define INPORT(port) CONCAT(PIN, port)

#define OUTPORT(port) CONCAT(PORT, port)

/* Program-specific macros */

#define cam_clk_high() sbit(OUTPORT(CLK_PORT), CLK_PIN)

#define cam_clk_low() cbit(OUTPORT(CLK_PORT), CLK_PIN)

#define cam_si_high() sbit(OUTPORT(SI_PORT), SI_PIN)

#define cam_si_low() cbit(OUTPORT(SI_PORT), SI_PIN)

static int usart_putchar(char c, FILE *stream);

static FILE mystdout = FDEV_SETUP_STREAM(usart_putchar, NULL, _FDEV_SETUP_WRITE);

/* Global variables */

volatile unsigned char _integrationTime = 10; // in milliseconds

unsigned char _data[128];

// Send char over USART

static int usart_putchar(char c, FILE *stream) {

// add '\r' before '\n'

//if (c == '\n') usart_putchar('\r', stream);

// wait for empty transmit buffer

while ( !(UCSR0A & (1 << UDRE0)) );

// send char

UDR0 = c;

return 0;

}

// Send char over USART

void usart_send_char(unsigned char ch) {

// wait for empty transmit buffer

while ( !(UCSR0A & (1 << UDRE0)) );

// send char

UDR0 = ch;

}

// Read the 8 most significant bits

// of the AD conversion result

unsigned char read_adc() {

// Start the AD conversion

ADCSRA |= (1 << ADSC);

// Wait for the AD conversion to complete

while ((ADCSRA & (1 << ADIF)) == 0);

// Clear flag

ADCSRA |= (1 << ADIF);

return ADCH;

}

// RX Complete handler

ISR (USART_RX_vect) {

// received character is set as integration time in [ms], max 100

unsigned char ch;

ch = UDR0;

if (ch > 100) ch = 100;

_integrationTime = ch;

}

// Main loop

int main(void)

{

// Pin config

sbit(DDR(CLK_PORT), CLK_PIN); // CLK out

sbit(DDR(SI_PORT), SI_PIN); // SI out

cbit(DDR(A0_PORT), A0_PIN); // analog in

// Configure UART

// - parameters: 8 Data, 1 Stop, No Parity

// - baud rate: 19200

UCSR0B = (1 << RXCIE0) | (1 << RXEN0) | (1 << TXEN0);

UCSR0C = (1 << UCSZ01) | (1 << UCSZ00);

UBRR0 = 51; // @16MHz, 0.2% error

// ADC initialization

// - ADC clock frequency: F_CPU / 128 (125kHz @ 16MHz)

// - reference: AVcc with external cap

// - channel: as defined in A0_PIN

// - result left adjusted!

ADMUX = (1 << REFS0) | (1 << ADLAR) | A0_PIN;

ADCSRA = (1 << ADEN) | (1 << ADPS2) | (1 << ADPS1) | (1 << ADPS0);

// Redirect STDOUT to USART

stdout = &mystdout;

// Interrupt global enable

sei();

// Init StampPlot

printf("!PNTS 128\r");

printf("!PLOT ON\r");

printf("!MAXR\r");

printf("!AMAX 255\r");

printf("!TMAX 1\r");

printf("!RSET\r");

// some delay for PC port buffers to clear

_delay_ms(500);

// time to send

unsigned char tts = 0;

while(1)

{

cam_si_high();

cam_clk_high();

cam_si_low();

unsigned char i;

for (i = 0; i < 128; i++)

{

cam_clk_low();

unsigned char val = read_adc();

_data[i] = val;

cam_clk_high();

}

cam_clk_low();

// delay for integration time

for (i = 0; i < _integrationTime; i++) _delay_ms(1);

// send data

if (tts++ == 10)

{

tts = 0;

// data send lasts ~150ms

for (i = 0; i < 128; i++) printf("%d\r", _data[i]);

}

}

}

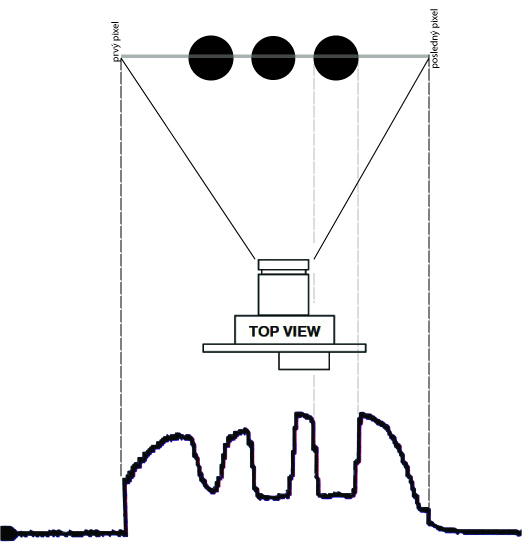

Snímaný obrázok a výsledky

Pomocou riadkovej kamery TSL1410_DB sme skúšali snímať rôzne predmety a zobrazovať priebehy cez Stampplot. Pre lepšiu kvalitu zobrazenia sme si ale zvolili osciloskop, na ktorom sme si zobrazili výstupný signál A0 pri snímaní nasledujúceho obrázka.