1-Riadková kamera TSLR1401: Rozdiel medzi revíziami

Z SensorWiki

| Riadok 17: | Riadok 17: | ||

TSL1401_DB je lineárna kamera, ktorá sa skladá z poľa fotodiód 128 x 1. Vnútorná riadiaca logika kamery si vyžaduje pre správnu funkčnosť zapojenie sériového vstupu SI a hodinového signálu CLK. | TSL1401_DB je lineárna kamera, ktorá sa skladá z poľa fotodiód 128 x 1. Vnútorná riadiaca logika kamery si vyžaduje pre správnu funkčnosť zapojenie sériového vstupu SI a hodinového signálu CLK. | ||

| − | [[Súbor:TSL1410_DB.jpg| | + | [[Súbor:TSL1410_DB.jpg|100px|center]] |

<center>'''Obr. 1.''' Riadková kamera TSL1410_DB</center> | <center>'''Obr. 1.''' Riadková kamera TSL1410_DB</center> | ||

| Riadok 24: | Riadok 24: | ||

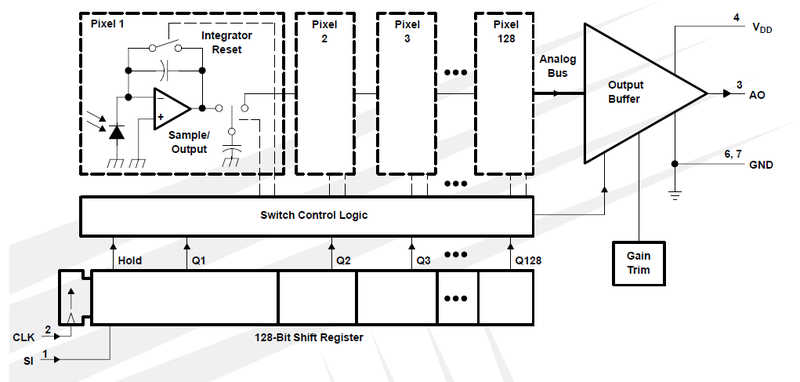

Na nasledujúcom obrázku je schéma zapojenia lineárnej kamery, vnútornej štruktúry a označenie jednotlivých pinov. | Na nasledujúcom obrázku je schéma zapojenia lineárnej kamery, vnútornej štruktúry a označenie jednotlivých pinov. | ||

| − | [[Súbor:funkcna_blokova_schema.jpg| | + | [[Súbor:funkcna_blokova_schema.jpg|800px|center]] |

<center>'''Obr. 2.''' Riadková kamera TSL1410_DB</center> | <center>'''Obr. 2.''' Riadková kamera TSL1410_DB</center> | ||

Verzia zo dňa a času 13:58, 22. december 2012

- Vypracovali:

- Bc. Peter Lovaš

- Bc. Tomáš Oravec

- Bc. Ján Mazúch

- Študijný odbor: Aplikovaná mechatronika

- Ročník: 2. Ing.

Zadanie úlohy

- Riadkovy senzor TSL1410_DB pripojte k mikroprocesoru, výstupný analógový signál preneste do PC a zobrazte.

Popis riadkovej kamery

TSL1401_DB je lineárna kamera, ktorá sa skladá z poľa fotodiód 128 x 1. Vnútorná riadiaca logika kamery si vyžaduje pre správnu funkčnosť zapojenie sériového vstupu SI a hodinového signálu CLK.

Na nasledujúcom obrázku je schéma zapojenia lineárnej kamery, vnútornej štruktúry a označenie jednotlivých pinov.