TTLogik príklady: Rozdiel medzi revíziami

Zo stránky SensorWiki

Bez shrnutí editace |

Bez shrnutí editace |

||

| Riadok 126: | Riadok 126: | ||

[[Súbor:D_ff2.png|450px]] | [[Súbor:D_ff2.png|450px]] | ||

</center> | |||

== 6. Klopný obvod typu JK == | |||

'''Cieľ úlohy:'''<br> | |||

:Preskúmať činnosť univerzálneho klopného obvodu typu JK a prakticky identifikovať jav pretekania. | |||

'''Teória:'''<br> | |||

:Obvod JK je najuniverzálnejší pamäťový prvok pretože pri súčasnej aktivácii oboch vstupov neguje svoj predchádzajúci stav. Kvôli vysokej rýchlosti logických hradiel však pri hladinovom riadení dochádza k rýchlym osciláciám ak je riadiaci impulz príliš dlhý. Tento jav sa nazýva pretekanie a spôsobuje že konečný stav obvodu je po uvoľnení tlačidla náhodný. Stabilitu jednotlivých impulzov zabezpečuje tlačidlo P ktoré generuje potrebný signál pre zmenu stavu. | |||

'''Úloha'''<br> | |||

:Na realizáciu tohto obvodu využite kombináciu trojvstupových hradiel NAND a dvojvstupových hradiel NAND. Dôsledne prepojte spätné väzby z výstupov späť na vstupy riadiacich hradiel podľa priloženej schémy. Overte stavy nastavenia a nulovania pomocou dátových prepínačov a tlačidla P. Sledujte ako obvod reaguje na jednotlivé impulzy a zaznamenajte výsledky do pravdivostnej tabuľky. | |||

<center> | |||

[[Súbor:JK_latch.png|500px]] | |||

</center> | </center> | ||

Verzia z 11:28, 5. marec 2026

Odkazy na obvody v simulátore TinkerCAD

Odkazy na obvody v EasyEDA

1. Zoznámenie sa so zariadením

Cieľ úlohy:

- Oboznámiť sa so základnými časťami experimentálneho kitu a pochopiť princíp zapájania obvodov na bezkontaktnom prepojovacom poli.

Teória:

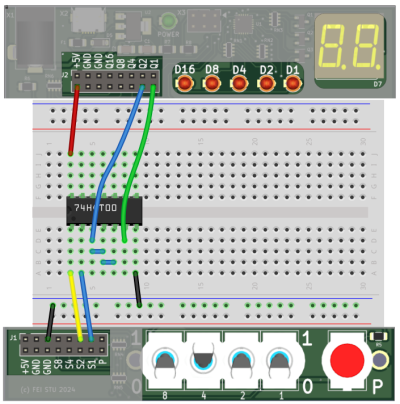

- Bezkontaktné pole umožňuje rýchle vytváranie a testovanie jednoduchých zapojení bez potreby spájkovania. Študenti si v tejto časti precvičia základné operácie ako pripojenie napájania a uzemnenia k integrovaným obvodom. Správna funkcia sa overuje prostredníctvom vstupných prepínačov a výstupných svetelných diód umiestnených na doske TTLkitu.

Úloha:

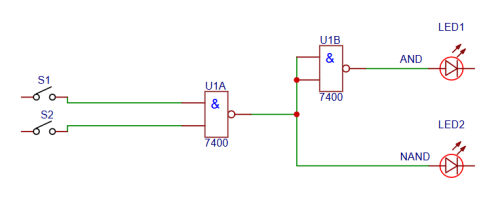

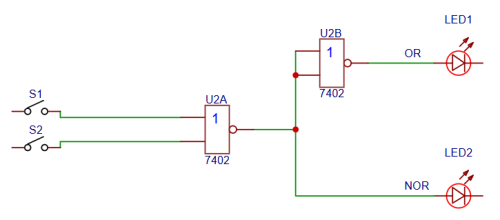

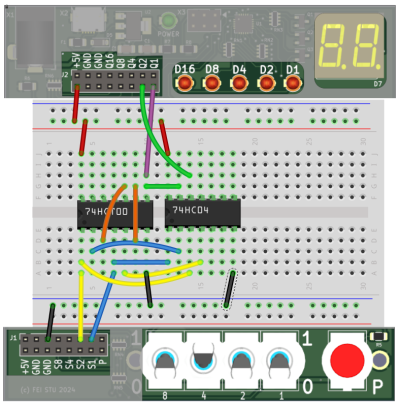

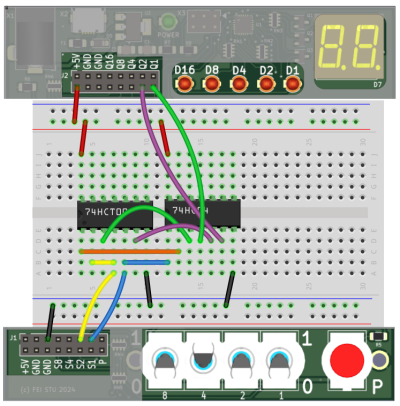

- Zapojte vybraný logický člen na skúšobnej doske a overte jeho funkciu pre všetky vstupné kombinácie. Práca prebieha s integrovaným obvodom 7400 pre hradlá NAND alebo s obvodom 7402 pre hradlá NOR. Po overení základnej funkcie pre všetky stavy rozšírte zapojenie o negáciu výstupu čím zrealizujete logickú funkciu AND v prípade hradiel NAND alebo funkciu OR pri využití hradiel NOR. Namerané výsledky zapíšte do pripravenej pravdivostnej tabuľky.

- Obvod SN74HCT00N - datasheet

2. Analýza logického obvodu

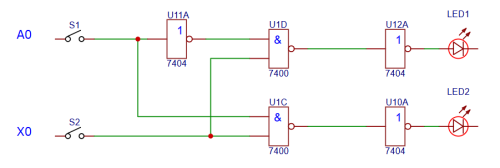

Cieľom tejto úlohy je analyzovať zložitejší logický obvod, ktorý pozostáva z viacerých logických členov typu NAND. Úlohou je pochopiť, ako sa hradlá kombinujú pre realizáciu konkrétnej funkcie a overiť jej správnosť meraním.

Zapojte na skúšobnej doštičke obvod podľa nasledovnej schémy zapojenia.

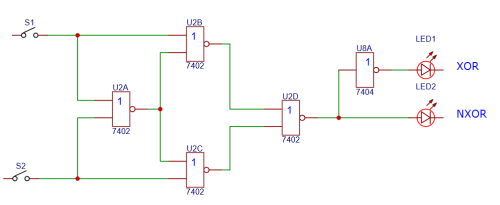

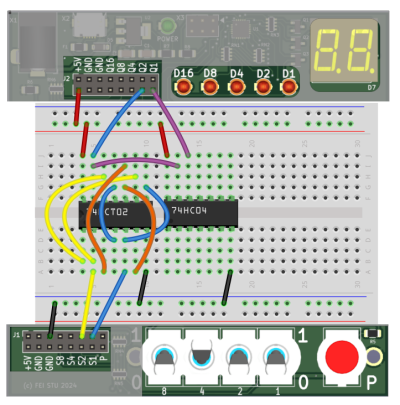

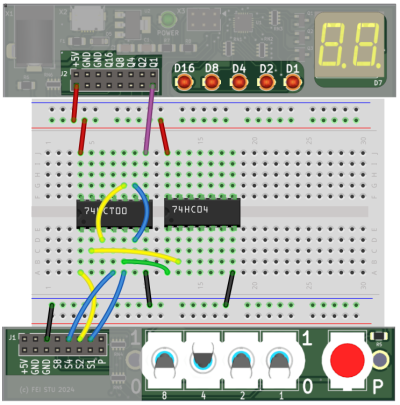

3. XOR a NXOR

Cieľ úlohy:

- Pochopiť a prakticky realizovať logické funkcie XOR a NXOR, ktoré patria medzi základné operácie v digitálnych systémoch. Cieľom je ukázať, že aj tieto zložitejšie funkcie je možné zostaviť z jednoduchých základných hradiel.

Teória:

- Funkcie XOR a NXOR sa často využívajú v obvodoch na porovnávanie signálov, pri aritmetických operáciách alebo pri generovaní paritných bitov. Ich implementácia z jednoduchých logických členov je dôležitým krokom pri návrhu komplexných digitálnych systémov. Realizácia pomocou univerzálnych hradiel NAND alebo NOR potvrdzuje ich schopnosť nahradiť akúkoľvek inú logickú funkciu.

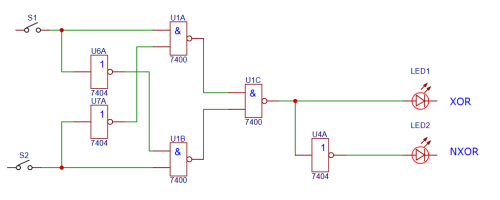

Časť 1: Realizácia pomocou hradiel NAND

- Zostavte logickú funkciu XOR s využitím integrovaného obvodu so štyrmi hradlami NAND. Po úspešnom overení funkcie rozšírte obvod o ďalšiu negáciu na výstupe, čím vytvoríte funkciu NXOR. Na testovanie použite vstupné tlačidlá a výsledný stav sledujte na svetelných diódach.

Časť 2: Realizácia pomocou hradiel NOR

- Postupujte analogicky ako v predchádzajúcej časti, avšak na vytvorenie logických vzťahov využite výhradne hradlá typu NOR. Overte všetky kombinácie vstupov a výsledky zapíšte do pripravenej pravdivostnej tabuľky pre obe funkcie. Porovnajte namerané hodnoty s teoretickými predpokladmi a overte správnosť zapojenia.

Poznámka: Pre jednoduchosť je v schémach použitý symbol pre logický člen NOT. Vy však namiesto neho môžete použiť aj voľné hradlo z obvodu NAND alebo NOR, ktoré zapojíte ako invertor.

4. Multiplexor a Demultiplexor

Cieľ úlohy:

- Pochopiť princíp fungovania multiplexora a demultiplexora ako základných prvkov pre smerovanie signálov v digitálnych systémoch. Cieľom je prakticky overiť, ako tieto obvody umožňujú efektívny výber a distribúciu dát.

Teória:

- Multiplexor (MUX) funguje ako elektronický prepínač, ktorý na základe riadiaceho vstupu vyberá jeden z viacerých vstupných signálov a prenáša ho na spoločný výstup. Demultiplexor (DMUX) vykonáva opačnú operáciu, kedy jeden vstupný signál rozdeľuje na viacero výstupov podľa stavu riadiaceho signálu. Tieto obvody sa v praxi využívajú pri prenose dát, adresovaní pamätí alebo pri riadení digitálnych zariadení.

Časť 1: Multiplexor 2:1

- Zostavte multiplexor 2 na 1 pomocou štyroch hradiel NAND z integrovaného obvodu 7400. Obvod má dva dátové vstupy (X0, X1) a jeden výberový vstup (A). Prepínačom A určujete, ktorý z dátových vstupov sa prenesie na výstup, zatiaľ čo ostatné vstupy zostávajú neaktívne. Výsledný stav sledujte pomocou LED diódy, ktorá zobrazuje aktuálnu logickú úroveň výstupu.

Časť 2: Demultiplexor 1:2

- Navrhnite a zapojte demultiplexor, ktorý rozdelí jeden dátový vstup (X) na dva výstupy (Y0, Y1) podľa riadiaceho vstupu. Takto získate prehľad o vzájomnej väzbe medzi oboma obvodmi a ich praktickom využití v digitálnych systémoch.

Poznámka: Pre realizáciu funkcie demultiplexora (ktorá vyžaduje logiku AND) pomocou hradiel NAND musíte na ich výstupy pridať negáciu.

5. Asynchrónny klopný obvod typu RS

Cieľ úlohy:

- Pochopiť princíp fungovania základnej pamäťovej bunky a overiť vplyv spätnej väzby na uchovávanie logického stavu aj po zániku vstupného signálu.

Teória:

- Klopný obvod typu RS je najjednoduchší sekvenčný obvod. Na rozdiel od bežných kombinačných obvodov jeho výstup závisí nielen od aktuálnych logických úrovní na vstupoch, ale aj od jeho vlastného predchádzajúceho stavu. Túto pamäťovú vlastnosť zabezpečuje krížová spätná väzba medzi použitými logickými hradlami. Tento obvod tvorí úplný základ pre zložitejšie pamäte a registre.

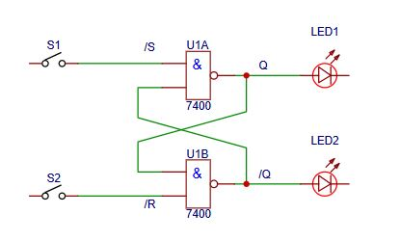

Úloha:

- Na realizáciu použite dva dvojvstupové logické členy NAND v obvode 7400. Nezabudnite na pripojenie napájania Vcc na pin 14 a GND na pin 7.

- Po zapojení pripojte na vstupy prepínače S1 a S2 a na výstupy LED diódy D1 a D2. Vyskúšajte všetky kombinácie vstupov a výsledky zapíšte do tabuľky. Zamerajte sa najmä na stav, kedy sú oba vstupy v logickej nule. Ako sa vtedy správajú výstupné diódy a prečo sa tento stav nazýva zakázaný?

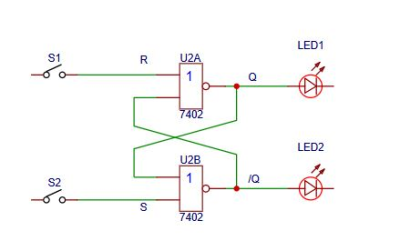

Bónus

- Ako bónusovú aktivitu sa pokúste zrealizovať rovnakú funkciu preklápacieho obvodu s využitím logických členov typu NOR v obvode 7402. Pri tomto zapojení sledujte rozdiel v aktívnych logických úrovniach na vstupoch a identifikujte, ktorá kombinácia v tomto prípade predstavuje zakázaný stav. Namerané výsledky následne porovnajte s predchádzajúcim zapojením vytvoreným z hradiel NAND.

5. Klopný obvod typu D

Cieľ úlohy:

- Pochopiť princíp fungovania pamäťového obvodu typu D a overiť rozdiel medzi hladinovo riadeným a impulzom riadeným zápisom dát.

Teória:

- Klopný obvod typu D odstraňuje problém zakázaného stavu tým že na vstupy vnútornej pamäťovej bunky privádza vždy opačné signály. Tento obvod slúži ako základná pamäť v digitálnych systémoch. Pri práci s týmto obvodom je dôležitá stabilita hodinového signálu ktorú na našom kite zabezpečuje tlačidlo Pulz s hardvérovo ošetrenými zákmity kontaktov.

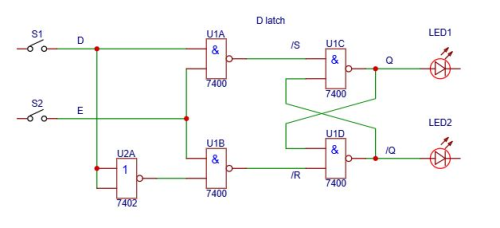

Časť 1: Hladinovo riadený obvod D latch

- Zostavte obvod podľa prvej schémy s použitím hradiel NAND z obvodu 7400 a jedného hradla NOR z obvodu 7402 zapojeného ako invertor. Na dátový vstup pripojte prepínač S1 a na povoľovací vstup prepínač S2. Overte transparentný režim kedy výstup priamo kopíruje zmeny na vstupe a následne vyskúšajte režim pamätania po deaktivácii riadiaceho signálu.

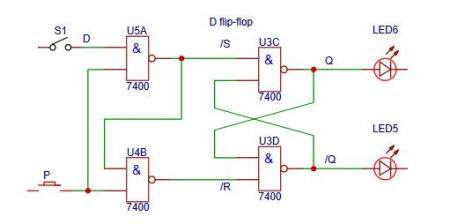

Časť 2: Impulzom riadený obvod D flip-flop

- V druhej časti zostavte obvod podľa druhej schémy s využitím hradiel NAND. Na dátový vstup pripojte prepínač S1 a na riadenie zápisu využite tlačidlo P. Overte že sa nová hodnota zapíše do pamäte až po vygenerovaní impulzu a že obvod si uchováva poslednú zapísanú hodnotu aj po ďalšej zmene dátového vstupu.

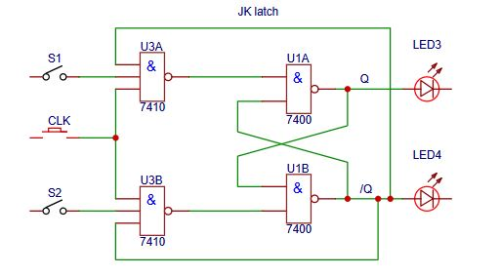

6. Klopný obvod typu JK

Cieľ úlohy:

- Preskúmať činnosť univerzálneho klopného obvodu typu JK a prakticky identifikovať jav pretekania.

Teória:

- Obvod JK je najuniverzálnejší pamäťový prvok pretože pri súčasnej aktivácii oboch vstupov neguje svoj predchádzajúci stav. Kvôli vysokej rýchlosti logických hradiel však pri hladinovom riadení dochádza k rýchlym osciláciám ak je riadiaci impulz príliš dlhý. Tento jav sa nazýva pretekanie a spôsobuje že konečný stav obvodu je po uvoľnení tlačidla náhodný. Stabilitu jednotlivých impulzov zabezpečuje tlačidlo P ktoré generuje potrebný signál pre zmenu stavu.

Úloha

- Na realizáciu tohto obvodu využite kombináciu trojvstupových hradiel NAND a dvojvstupových hradiel NAND. Dôsledne prepojte spätné väzby z výstupov späť na vstupy riadiacich hradiel podľa priloženej schémy. Overte stavy nastavenia a nulovania pomocou dátových prepínačov a tlačidla P. Sledujte ako obvod reaguje na jednotlivé impulzy a zaznamenajte výsledky do pravdivostnej tabuľky.