FPGA: Rozdiel medzi revíziami

Zo stránky SensorWiki

Bez shrnutí editace |

|||

| Riadok 7: | Riadok 7: | ||

== Intel == | == Intel == [[Súbor:logoAltera.png|right|250px]] | ||

| Riadok 17: | Riadok 17: | ||

== Lattice == | [[Súbor:Intel-DE10-lite-board.jpg|center|300px]] | ||

== Lattice == [[Súbor:logoLattice.png|right|250px]] | |||

* Software: | * Software: | ||

** | ** | ||

** Open Source [https://icestudio.io/ IceStudio] - graficky editor | ** Open Source [https://icestudio.io/ IceStudio] - graficky editor | ||

== Infineon (was: Cypress) == | == Infineon (was: Cypress) == [[Súbor:logoCypress.png|right|250px]] | ||

Aj s analogovymi blokmi | Aj s analogovymi blokmi | ||

Verzia z 09:06, 29. január 2023

FPGA = Field programmable gate array (Wikipedia)

CPLD = Complex Programmable Logic Device (wikipedia)

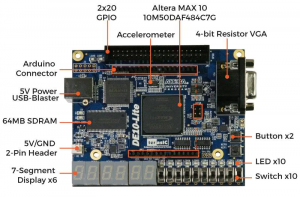

Súbor:CPLDboard.jpg - sem pride obrazok tej CPLD dosky ktoru uz mame

== Intel ==

- Software:

- Quartus

- Arduino MKR Vidor4000 (Intel® Cyclone® 10CL016 + Cortex-M0 32-bit SAMD21)

== Lattice ==

- Software:

- Open Source IceStudio - graficky editor

== Infineon (was: Cypress) ==

Aj s analogovymi blokmi

- https://www.infineon.com/cms/en/product/evaluation-boards/cy8ckit-059/ (Arm Cortex M3 alebo 8051 vo vnutri?)

Jazyky

- ABEL (ten ktory sme pouzivali na GAL obvody) - velmi jednoduchy a velmi low-level. Niektore starsie kompilatory ho poznaju

- Verilog (zda sa celkom zrozumitelny)

- VHDL

- ? ktovie ako je to s prekladom KiCAD -> HDL pretoze napr. Lattice v poslednej verzii uz graficky navrh vyhodili

Verliog a VHDL su jazyky na simulaciu digitalnych obvodov, preto aj Verilog ma velmi podobne prikazy na popis HW ale aj na signaly a vieme tak opisat rovnakym jazykom nielen obvod, ale aj stimuly ktorymi ho budeme testovat.

Literatura

- Best: Wakerly: 'Digital Design'.